# National Semiconductor

# DP84322 Dynamic RAM Controller Interface Circuit for the 68000 CPU

### **General Description**

The DP84322 dynamic RAM controller interface is a Programmable Array Logic (PAL®) device which allows for easy interface between the DP8409A, 17, 18, 19, 28, 29 dynamic RAM Controllers and the 68000/008/010 microprocessors.

The DP84322 supplies all the control signals needed to perform memory read, write and refresh. Logic is included for inserting a wait state when using fast CPUs.

#### **Features**

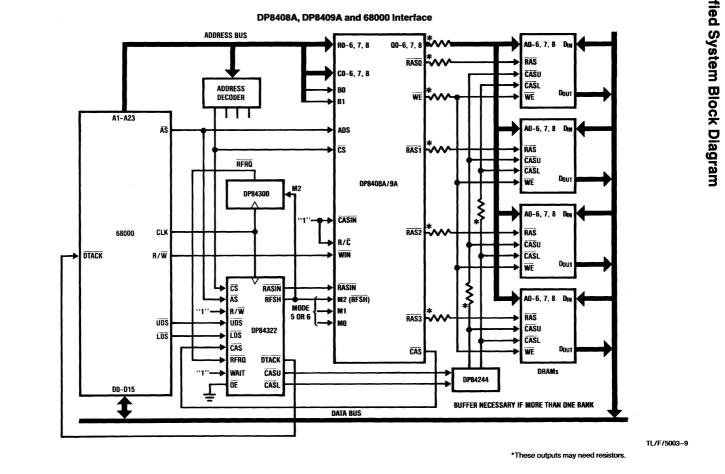

- Provides 3-chip solution for the 68000 CPU and dynamic RAM interface (DP84300, DP84322, & DP8409A)

- Works with all 68000 speed versions

- Possibility of operation at 8 MHz with no wait states

- Performs hidden refresh

- DTACK is automatically inserted for both memory access and memory refresh

- Performs forced refresh using typically 4 CPU clocks

- Standard National Semiconductor PAL part (DMPAL16R4)

- PAL logic equations can be modified by the user for his specific application and programmed into any of the PAL in the National Semiconductor PAL family, including the new high speed PALs.

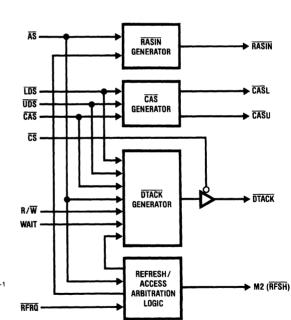

### **Connection and Block Diagrams**

TL/F/5003-2

# Recommended Operating Conditions (Commercial) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                                    | Min | Тур |

|----------------------------------------------------|-----|-----|

| T <sub>A</sub> , Operating Free Air<br>Temperature | 0   |     |

|                                                    |     |     |

|                                             | Min  | Тур  | Max     | Units |

|---------------------------------------------|------|------|---------|-------|

| V <sub>CC</sub> , Supply Voltage            | 4.75 | 5.00 | 5.25    | V     |

| I <sub>OH</sub> , High Level Output Current |      |      | -3.2    | mΑ    |

| IOL, Low Level Output Current               |      |      | 24      | mA    |

|                                             |      |      | (Note 2 | )     |

## Electrical Characteristics over recommended operating temperature range

| Symbol           | Parameter                                              | Conditions                                               | Min | Тур | Max    | Units |

|------------------|--------------------------------------------------------|----------------------------------------------------------|-----|-----|--------|-------|

| VIH              | High Level Input Voltage                               |                                                          | 2   |     |        | V     |

| VIL              | Low Level Input Voltage                                |                                                          |     |     | 0.8    | V     |

| VIC              | Input Clamp Voltage                                    | $V_{CC} = Min, I_I = -18 \text{ mA}$                     |     |     | -1.5   | V     |

| V <sub>OH</sub>  | High Level Output Voltage                              | $V_{CC} = Min, V_{IH} = 2V, V_{IL} = 0.8V, I_{OH} = Max$ | 2.4 |     |        | V     |

| V <sub>OL</sub>  | Low Level Output Voltage                               | $V_{CC} = Min, V_{IH} = 2V, V_{IL} = 0.8V, I_{OL} = Max$ |     |     | 0.5    | ٧     |

| lozh             | Off-State Output Current<br>High Level Voltage Applied | $V_{CC} = Max, V_{IH} = 2V, V_O = 2.4V, V_{IL} = 0.8V$   |     |     | 100    | μΑ    |

| I <sub>OZL</sub> | Off-State Output Current<br>Low Level Voltage Applied  | $V_{CC} = Max, V_{IH} = 2V, V_O = 0.4V, V_{IL} = 0.8V$   |     |     | - 100  | μΑ    |

| h                | Input Current at<br>Maximum Input Voltage              | $V_{CC} = Max, V_I = 5.5V$                               |     |     | 1.0    | mA    |

| IIH              | High Level Input Current                               | $V_{CC} = Max, V_I = 2.4V$                               |     |     | 25     | μA    |

| Ι <sub>ΙL</sub>  | Low Level Input Current                                | $V_{CC} = Max, V_I = 0.4V$                               |     |     | -250   | μΑ    |

| los              | Short Circuit Output Current                           | V <sub>CC</sub> = Max                                    | -30 |     | - 130  | mA    |

| lcc              | Supply Current                                         | V <sub>CC</sub> = Max                                    |     | 150 | 225(1) | mA    |

#### Switching Characteristics over recommended ranges of temperature and V<sub>CC</sub> (Note 3)

| Symbol           | Paramete                 | r                      | Test Conditions $R_L = 667\Omega$ |     | Units |     |    |

|------------------|--------------------------|------------------------|-----------------------------------|-----|-------|-----|----|

|                  |                          |                        |                                   | Min | Тур   | Max |    |

| t <sub>PD</sub>  | Input to Output          |                        | C <sub>L</sub> = 50 pF            |     | 15    | 25  | ns |

| t <sub>PD</sub>  | Clock to Output          |                        |                                   |     | 10    | 15  | ns |

| t <sub>PZX</sub> | Pin 11 to Output Er      | nable                  |                                   |     | 10    | 20  | ns |

| t <sub>PXZ</sub> | Pin 11 to Output Disable |                        | $C_L = 5  pF$                     |     | 11    | 20  | ns |

| t <sub>PZX</sub> | Input to Output Ena      | Input to Output Enable |                                   |     | 10    | 25  | ns |

| t <sub>PXZ</sub> | Input to Output Disable  |                        | C <sub>L</sub> = 5 pF             |     | 13    | 25  | ns |

| t <sub>w</sub>   | Width of Clock High      |                        |                                   | 15  |       |     | ns |

|                  |                          | Low                    |                                   | 15  |       |     | ns |

| t <sub>su</sub>  | Set-Up Time              |                        |                                   | 25  |       |     | ns |

| t <sub>h</sub>   | Hold Time                |                        |                                   | 0   | -10   |     | ns |

Note 1:  $I_{CC} = \max$  at minimum temperature.

Note 2: One output at a time; otherwise 16 mA.

Note 3: If a PAL16R4B PAL is used, the Switching Characteristics will improve correspondingly.

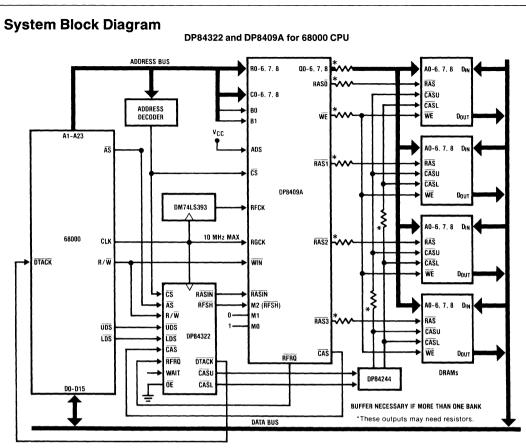

TL/F/5003-3

#### **Mnemonic Description**

#### INPUT SIGNALS

- CLOCK The clock signal determines the timing of the outputs and should be connected directly to the 68000 clock input.

- AS Address Strobe from the 68000 CPU. This input is used to generate RASIN to the DP8409A.

- UDS, LDS Upper and lower data strobe from the 68000 CPU. These inputs, together with AS, R/W, provide DTACK to the 68000.

- $R/\overline{W}$  Read/write from the 68000 CPU, when WAIT = 0. Selects processor speed when WAIT = 1 ("1" = 4 to 6 MHz, "0" = 8 MHz).

- CAS Column Address Strobe from the DP8409A. This input, together with LDS and UDS, provides two separate CAS outputs for accessing upper and lower memory data bytes.

- RFRQ Refresh Request. This input requests the DP84322 for a forced refresh.

- WAIT This input allows the necessary wait state to be inserted for memory access cycles.

#### **OUTPUT SIGNALS**

- RASIN

This output provides a memory cycle start signal to the DP8409A and provides RAS timing during hidden refresh.

- RFSH This output controls the mode of the DP8409A. It always goes low for 4 CPU clock periods when AS is inactive and a forced refresh is requested through RFRQ input. This allows the DP8409A to perform an automatic forced refresh.

#### Functional Description

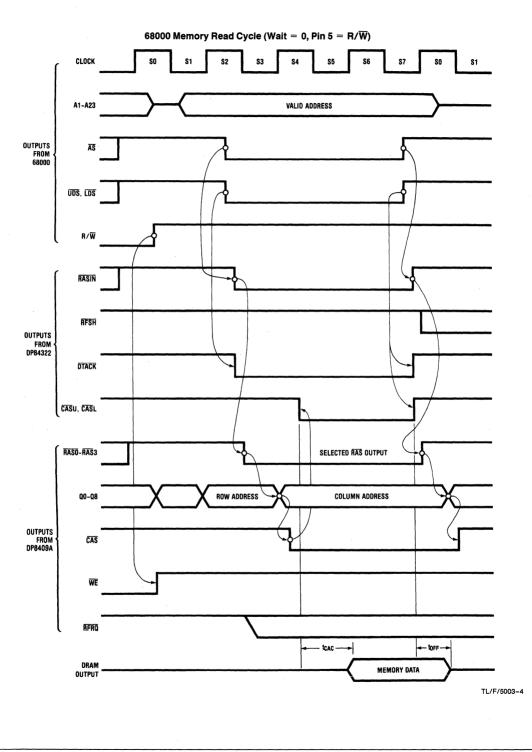

#### MEMORY ACCESS

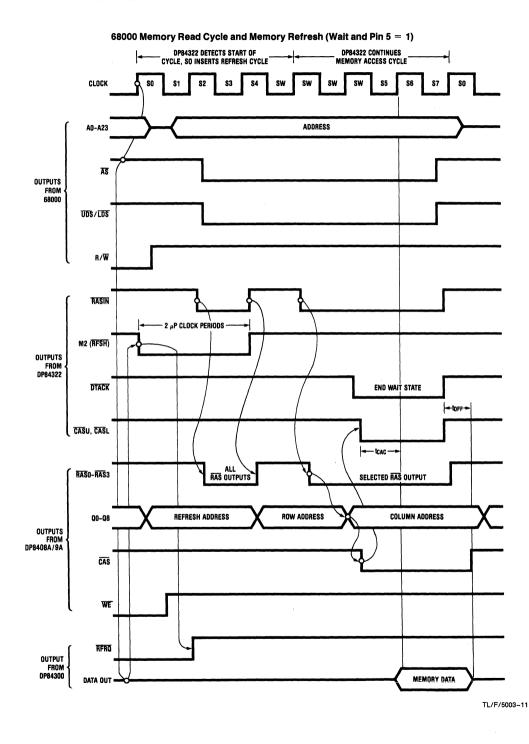

As a 68000 bus cycle begins, a valid address is output on the address bus A1-A23. This address is decoded to provide Chip Select (CS) to the DP8409A. After the address becomes valid. AS goes low and it is used to set RASIN low from the DP84322 interface circuit. Note that CS must go low for a minimum of 10 ns before the assertion of RASIN for a proper memory access. As an example, with a 8 MHz 68000, the address is valid for at least 30 ns before AS goes active. AS then has to ripple through the DP84322 to produce RASIN. This means the address is valid for a minimum of 40 ns before RASIN goes low, and the decoding of CS should take less than 30 ns. At this speed the DM74LS138 or DM74LS139 decoders can be selected to guarantee the 10 ns minimum required by CS set-up time going low before the access RASIN goes low (t<sub>CSBI</sub> of the DP8409A). This is important because a false hidden refresh may take place when the minimum t<sub>CSRL</sub> is not met. Typically RASIN occurs at the end of S2. Subsequently, selected RAS output, row to column select and then CAS will automatically follow RASIN as determined by mode 5 of the DP8409A. Mode 5 guarantees a 30 ns minimum for row address hold time (tRAH) and a minimum of 8 ns column address set-up time (tASC). If the system requires instructions that use byte writing, then CASU and CASL are needed for accessing upper and lower memory data bytes, and they are provided by the DP84322. In the DP84322, LDS and UDS are gated with CAS from the DP8409A to provide CASL and CASU, therefore designers need not be concerned about delaying CAS during write cycles to assure valid data being written into memory. The 8 MHz 68000 specifies during a write cycle that data output is valid for a minimum of 30 ns before DS goes active. Thus, CASL and CASU will not go low for at least 40 ns after the output data becomes stable, guaranteeing the 68000 valid data is written to memory.

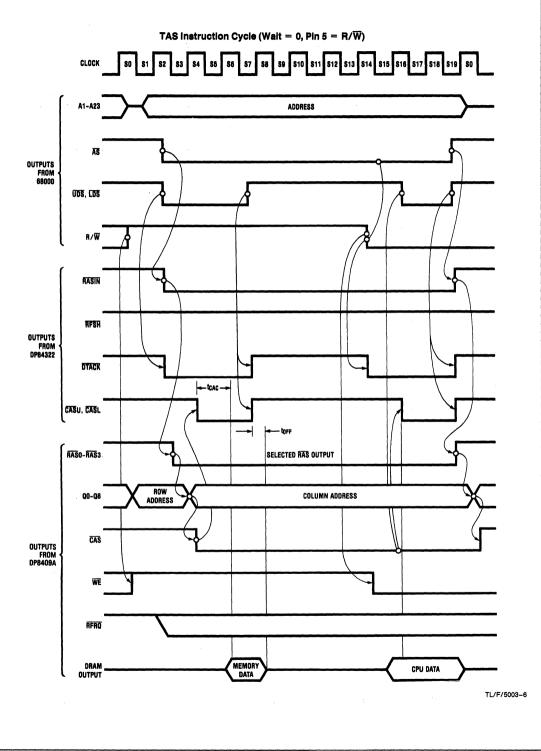

Furthermore, the gating of UDS, LDS and CAS allows the DP84322 interface controller to support the test and set instruction (TAS). The 68000 utilizes the read-modify-write cycle to execute this instruction. The TAS instruction provides a method of communication between processors in a multiple processor system. Because of the nature of this instruction, in the 68000, this cycle is indivisible and the Address Strobe AS is asserted throughout the entire cycle, however DS is asserted twice for two accesses: a read then a write. The dynamic RAM controller and the DP84322 respond to this read-modity-write instruction as follows (refer to the TAS instruction timing diagram for clarification). First, the selected RAS goes low as a result of AS going low, and this RAS output will remain low throughout the entire cycle. Then the DP84322's selected CAS output (CASL or CASU) goes low to read the specified data byte. After this read, DS ages high causing the selected CAS to go high. A few clocks later R/W goes low and then DS is reasserted. As DS goes low, the selected CAS goes low strobing the CPU's modified data into memory, after which the cycle is ended when AS goes high.

The two CAS outputs from the DP84322, however, can only drive one memory bank. For additional driving capability, a memory driver such as the DP84244 should be added to drive loads of up to 500 pF.

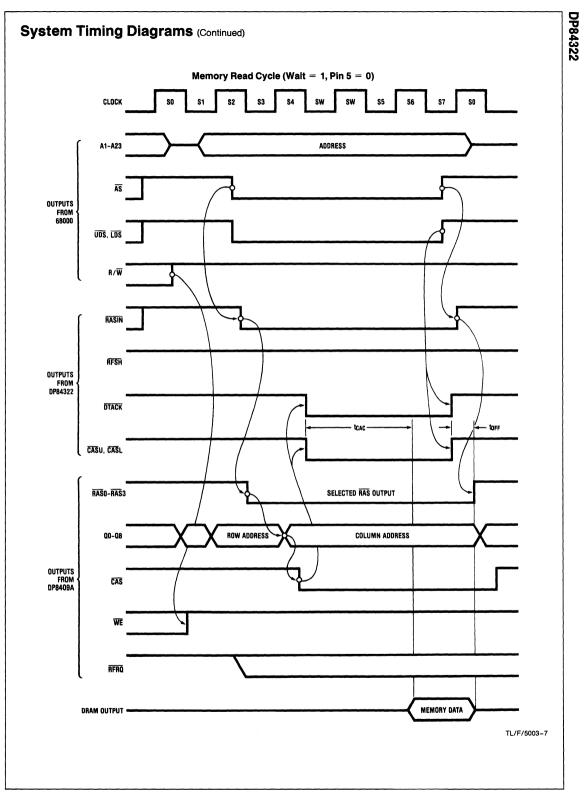

Since this DP84322 interface circuit is designed to operate with all of the 68000 speed versions, a status input called WAIT is used to distinguish the 8 MHz from the others. The WAIT input should be set low for 6 MHz or less allowing full speed of operation with no wait states. Data Transfer Acknowledge input (DTACK) of the 68000 at these speeds is automatically inserted during S2 for every memory transaction cycle and is then negated at the end of that cycle when UDS and/or LDS go high. For the 8 MHz 68000 however, a wait state is required for every memory transaction cycle. At these speeds, the WAIT input is set high, selecting the DP8409A's CAS output to generate DTACK and again DTACK is negated at the end of the cycle when UDS or LDS goes high. Note that DTACK output is enabled only when the DP8409A's CS is low. Therefore when the 68000 is accessing I/O or ROM (in other words, when the DP8409A is not selected), the DP84322's DTACK output goes high impedance logic '1' through the external pull-up resistor and it is now up to the designer to supply DTACK for a proper bus cycle.

The following table indicates the maximum memory speed in terms of the DRAM timing parameters: t<sub>CAC</sub> (access-time from CAS) and tRP (RAS precharge time) required by different 68000 speed versions:

| Microprocessor | Maximum          | Minimum         | Minimum |

|----------------|------------------|-----------------|---------|

| Clock          | <sup>t</sup> CAC | t <sub>RP</sub> | tRAS    |

| 8 MHz          | 125 ns           | 140 ns          | 220 ns  |

| 6 MHz          | 90 ns            | 170 ns          | 290 ns  |

| 4 MHz          | 270 ns           | 280 ns          | 450 ns  |

Pin 5 (R/W input to the DP84322) is not used as R/W when the WAIT input is high. Therefore, when WAIT is high and pin 5 is low, this is configured for the 8 MHz 68000. The dynamic RAM controller in this configuration operates in mode 5 and mode 1.

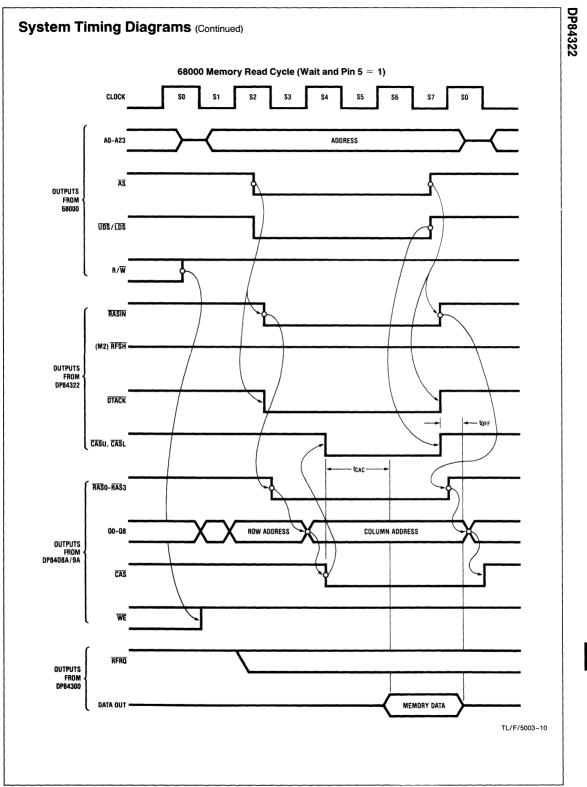

When both WAIT and pin 5 are high, this is configured for 4 MHz and 6 MHz 68000, allowing only two microprocessor clocks for memory refresh. Furthermore, the designer can use the DP8408A because the dynamic RAM controller now operates in mode 0 and mode 5 or mode 6. In addition, the programmable refresh timer, DP84300, should be used to determine the refresh rate (RFCK) and to provide the refresh request (RFRQ) input to the DP84322. The refresh timer can provide over two hundred different divisors. RFRQ is given at the beginning of every RFCK cycle and remains active until M2 goes low for memory refresh. The DP84322 samples RFRQ when AS is high, then sets M2 low for two microprocessor clocks, taking the DP8408A or DP8409A to the external control refresh mode. RASIN for this refresh is also issued by the DP84322. If a memory access is pending, RASIN for this access will not be given until it is delayed for approximately one microprocessor clock, allowing RAS precharge time for the dynamic RAMs.

The following table indicates different memory speeds in terms of the DRAM parameters required by 4 MHz and 6 MHz 68000:

#### Microprocessor Maximum Minimum Minimum Minimum

| Clock            | t <sub>CAC</sub> | tRAS         | t <sub>RP</sub> | t <sub>RAH</sub> |

|------------------|------------------|--------------|-----------------|------------------|

| 4 MHz            | 290 ns           | 200 ns       | 225 ns          | 20 ns            |

| 6 MHz            | 110 ns           | 125 ns       | 140 ns          | 20 ns            |

| DP8408A, DP8409A | operate in mor   | le 6 and mod | e 0.            |                  |

#### Functional Description (Continued)

When WAIT = 1, pin 5 = 0 (8 MHz), the PAL controller supports read and write cycles with one inserted wait state, forced refresh with five wait states inserted if  $\overline{CS}$  is valid, and hidden refresh. This PAL mode does not support the TAS instruction.

When WAIT = pin 5 = 1 (4–6 MHz), the PAL controller supports read and write cycles with no wait states inserted, and forced refresh with two wait states inserted if  $\overline{CS}$  is valid. This PAL mode does not support the TAS instruction and only supports hidden refresh when used in mode 5 with the DP8409A controller.

The DP84322 can possibly be operated at 8 MHz with no wait states (WAIT = "0") given the following conditions: FAST PAL (PAL16R4A)

S2 + S3 + S4 + S5 = 250 ns

$\overline{\text{RASIN}}$  delay = 60 ns ( $\overline{\text{AS}}$  low max.)

+ 25 ns (Fast PAL delay) = 85 ns max.

$\overline{\text{RASIN}}$  to  $\overline{\text{CAS}}$  delay DP8409-2 = 130 ns max.

External CASH, L generation using 74S02 and 74S240

7.5 ns (74S02) + 10 ns (74S240) - 7.5 ns (less load

on 8409  $\overline{CAS}$  line) = 10 ns max.

Transceiver delay (74LS245) = 12 ns max.

68000 data setup into S6 = 40 ns min.

∴ Minimum t<sub>CAC</sub> = 53 ns

= 250 - 85 - 130 - 10 - 12 + 40

Minimum t<sub>RAS</sub> = 240 ns

Minimum t<sub>BP</sub> = 150 ns

Minimum t<sub>RAH</sub> = 20 ns

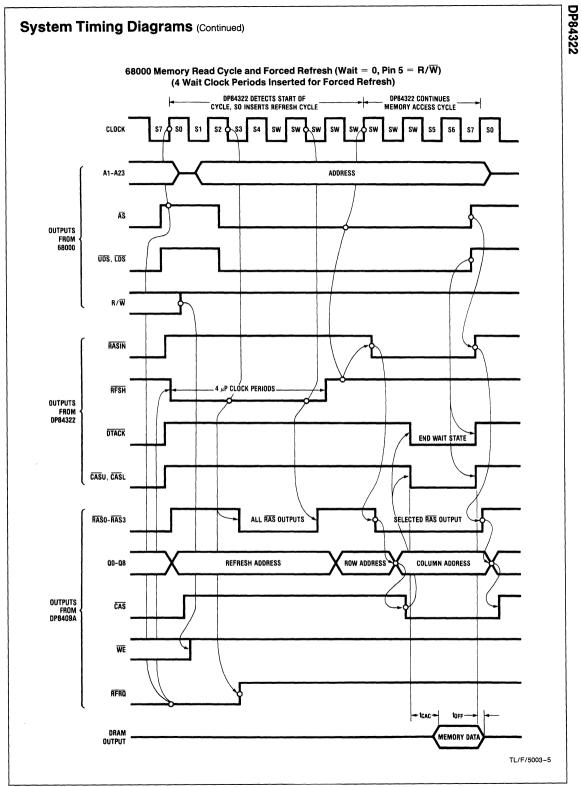

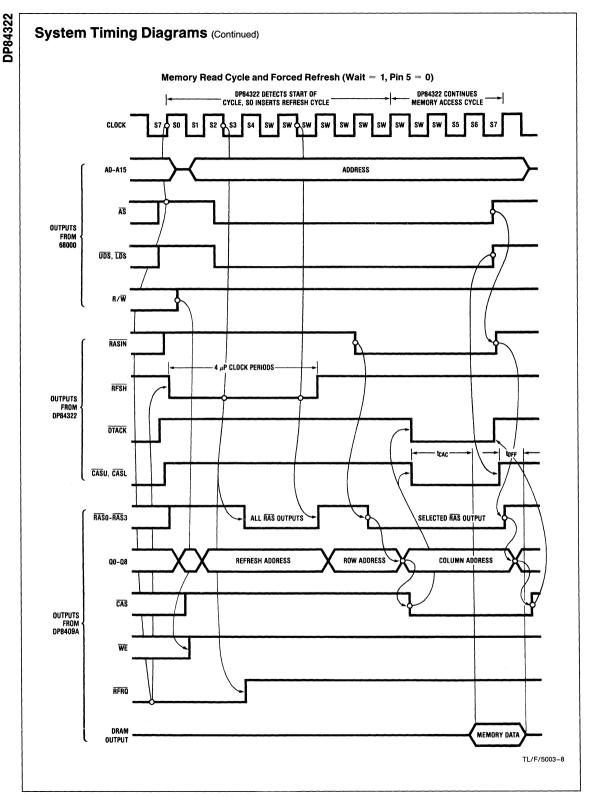

#### **REFRESH CYCLE**

Since the access sequence timing is automatically derived from RASIN in mode 5, R/C and CASIN are not used and now become Refresh Clock (RFCK) and RAS-generator clock (RGCK) respectively. The Refresh Clock RFCK may be divided down from RGCK, which is the microprocessor clock, using the DM74LS393 or DM74LS390. RFCK provides the refresh time interval and RGCK the fast clock for all-RAS refresh if forced refreshing is necessary. The DP8409A offers both hidden refresh in mode 5 and forced refreshesh in mode 1 with priority placed on hidden refreshing. Assume 128 rows are to be refreshed, then a 16  $\mu$ s maximum clock period is needed for RFCK to distribute refreshing of all the rows over the 2 ms period.

The DP8409A provides hidden refreshing in mode 5 when the refresh clock (RFCK) is high and the microprocessor is not accessing RAM. In other words, when the DP8409A's chip select is inactive because the microprocessor is accessing elsewhere, all four  $\overline{\text{RAS}}$  outputs follow  $\overline{\text{RASIN}}$ , strobing the contents of the on-chip refresh counter to every memory bank.  $\overline{\text{RASIN}}$  going high terminates the hidden refresh and also increments the refresh counter, preparing it for the next refresh cycle. Once a hidden refresh has taken place, a forced refresh will not be requested by the DP8409A for the current RFCK cycle.

However, if the microprocessor continuously accessed the DP8409A and memory while RFCK was high, a hidden refresh could not have taken place and now the system must force a refresh. Immediately after RFCK goes low, the Refresh Request signal (RFRQ) from the DP8409A goes low, indicating a forced refresh is necessary. First, when RFRQ goes low any time during S2 to S7, the controller interface circuit waits until the end of the current memory access cycle and then sets M2 (RFSH) low. This refresh takes four microprocessor clocks to complete. If the current cycle is another memory cycle, the 68000 will automatically be put in four wait states. Alternately, when RFRQ goes low while AS is high during S0 to S1, M2 is now set low at S2. Therefore, it requires an additional microprocessor clock for this refresh. Once the DP8409A is in mode 1 forced refresh, all the RAS outputs remain high until two RGCK trailing edges after M2 goes low, when all RAS outputs go low. This allows a minimum of one and a half clock periods of RGCK for RAS precharge time. As specified in the DP8409A data sheet, the RAS outputs remain low for two clock periods of RGCK. The refresh counter is incremented as the RAS outputs go high. Once the forced refresh has ended, M2 is brought high, the DP8409A back to mode 5 auto access. Note that **RASIN** for the pending access is not given until it has been delayed for a full microprocessor clock, allowing RAS precharge time for the coming access.

If the 68000 bus is inactive (i.e., the 68000's instruction queue is full, or the 68000 is executing internal operations such as a multiply instruction, or the 68000 is in halt state ...) and a refresh has been requested, a refresh will also take place because  $\overline{\text{RFRQ}}$  is continuously sampled while  $\overline{\text{AS}}$  is high. Therefore, refreshing under these conditions will be transparent to the microprocessor. Consequently, the system throughput is increased because the DP84322 allows refreshing while the 68000 bus is inactive.

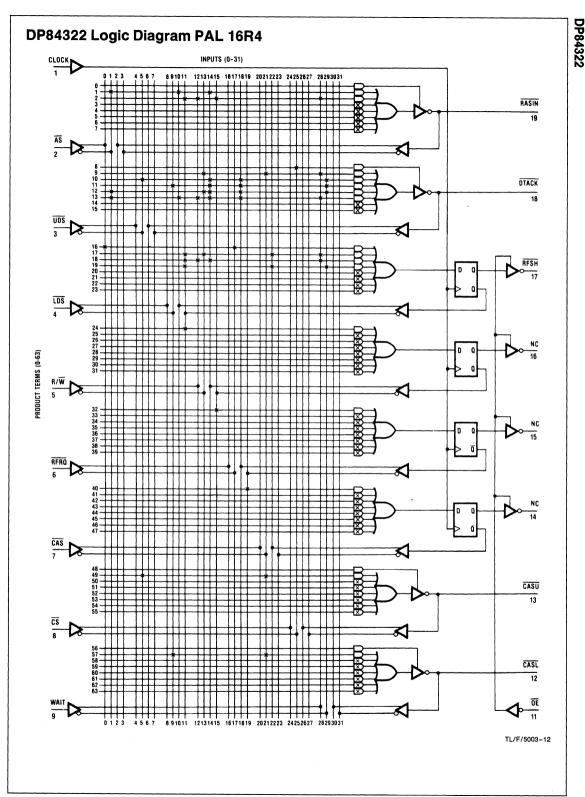

The 84322 is a standard National Semiconductor PAL part (DMPAL16R4). The user can modify the PAL equations to support his particular application. The 84322 logic equations function table (functional test), and logic diagram can be seen at the end of this data sheet.

# System Timing Diagrams

DP84322

3-15

# System Timing Diagrams (Continued)

DP84322

#### System Timing Diagrams (Continued)

**Modified System Block Diagram**

### **PAL Boolean Equations**

**DP84322**

PAL16R4 DP84322 Dynamic RAM Controller Interface for the MC68000-DP8409A Memory System CK /AS /UDS /LDS R /RFRQ /CAS /CS WAIT GND /OE /CL /CU /C /B /A /RFSH /DTACK /RASIN VCC IF (VCC) RASIN = AS • /RFSH • /A + RFSH • R • A • WAIT IF (CS) DTACK = /R • CAS • WAIT + UDS • /A • /B • /WAIT + LDS • /A • /B • /WAIT + AS • /R • /A • /B • /WAIT + AS • /RFSH • R • /A • /B • WAIT RFSH: = /AS • RFRQ + RFSH • /R • /C • WAIT + RFSH • R • /A • WAIT + RFSH • /C • /WAIT A: = RFSH B: = A C: = B IF (VCC) CL = UDS • CDS IF (VCC) CL = LDS • CAS

#### **Function Table**

| СК     | ĀS | UDS | LDS | R | RFRQ | CAS | CS | WAIT | ŌĒ | CL | CU | ī | B | Ā | RFSH | DTACK | RASIN |

|--------|----|-----|-----|---|------|-----|----|------|----|----|----|---|---|---|------|-------|-------|

| С      | н  | L   | L   | н | н    | н   | н  | L    | L  | н  | н  | х | х | х | х    | х     | н     |

| С      | н  | L   | L   | н | н    | L   | н  | L    | L  | L  | L  | Х | Х | Х | Х    | Х     | н     |

| С      | н  | L   | н   | н | н    | L   | н  | L    | L  | н  | L  | х | Х | Х | Х    | Х     | н     |

| С      | н  | н   | L   | н | н    | L   | н  | L    | L  | L  | Н  | Х | х | Х | Х    | Х     | н     |

| С      | н  | н   | н   | н | н    | н   | н  | L    | L  | н  | н  | н | н | н | н    | Z     | н     |

| С      | L  | L   | н   | н | н    | н   | L  | L    | L  | н  | н  | н | н | н | н    | L     | L     |

| С      | L  | L   | н   | н | н    | L   | L  | L    | L  | н  | L  | н | н | н | н    | L     | L     |

| С      | L  | н   | н   | н | н    | L   | L  | L    | L  | н  | н  | н | н | н | н    | н     | L     |

| С      | L  | н   | н   | L | н    | L   | L  | L    | L  | н  | н  | н | н | н | н    | L     | L     |

| С      | L  | L   | н   | L | н    | L   | L  | L    | L  | Н  | L  | н | н | н | н    | L     | L     |

| С      | н  | н   | н   | L | н    | н   | L  | L    | L  | Н  | н  | н | н | Н | н    | н     | н     |

| С      | н  | н   | н   | L | L    | н   | L  | L    | L  | Н  | н  | н | н | н | L    | н     | н     |

| С      | н  | н   | н   | L | L    | н   | L  | L    | L  | Н  | н  | н | н | L | L    | н     | н     |

| С      | L  | н   | L   | L | н    | н   | L  | L    | L  | н  | н  | н | L | L | L    | н     | н     |

| С      | L  | н   | L   | L | н    | н   | L  | L    | L  | н  | н  | L | L | L | L    | н     | н     |

| С      | L  | н   | L   | L | н    | н   | L  | L    | Ł  | н  | н  | L | L | L | ́ Н  | н     | н     |

| С      | L  | н   | L   | L | н    | н   | L  | L    | L  | н  | н  | L | L | н | н    | Н     | L     |

| С      | L  | н   | L   | L | н    | L   | L  | L    | L  | L  | н  | L | н | н | н    | L     | L     |

| С      | L  | н   | L   | L | н    | L   | Ŀ  | L    | L  | L  | н  | н | н | н | н    | L     | L     |

| С      | н  | н   | н   | L | н    | L   | Ŀ  | L    | L  | н  | н  | н | н | н | н    | н     | н     |

| С      | н  | н   | н   | L | L    | н   | L  | н    | L  | н  | Н  | н | н | Н | L    | н     | н     |

| С      | н  | н   | н   | L | L    | н   | L  | н    | L  | н  | н  | н | Н | L | L    | н     | н     |

| С      | L  | L   | L   | L | н    | н   | L  | н    | L  | н  | н  | н | L | L | L    | н     | н     |

| С      | L  | L   | L   | L | н    | н   | L  | н    | L  | н  | н  | L | L | L | L    | . Н   | н     |

| С      | L  | L   | L   | L | н    | н   | L  | н    | L  | н  | н  | L | L | L | н    | н     | н     |

| С      | L  | L   | L   | L | н    | н   | L  | н    | L  | н  | н  | L | L | н | н    | н     | L     |

| С      | L  | L   | L   | L | н    | L   | L  | н    | L  | L  | L  | L | н | н | н    | L     | L     |

| С      | н  | н   | н   | L | н    | L   | L  | н    | L  | н  | н  | н | н | н | н    | L     | н     |

| С      | н  | н   | н   | L | н    | н   | н  | н    | L  | н  | н  | н | н | н | н    | Z     | н     |

| С      | н  | н   | н   | н | L    | н   | L  | н    | L  | н  | н  | н | н | н | L.   | н     | н     |

| С      | н  | н   | н   | н | L    | н   | L  | н    | L  | н  | н  | н | н | L | L    | н     | L     |

| С      | L  | L   | н   | н | н    | н   | L  | н    | L  | н  | н  | н | L | L | н    | н     | н     |

| С      | L  | L   | н   | н | н    | н   | L  | н    | L  | н  | н  | L | L | н | н    | н     | L     |

| С      | L  | L   | н   | н | н    | L   | Ĺ  | н    | L  | н  | L  | L | н | н | н    | L     | L     |

| с<br>с | н  | н   | н   | н | н    | L   | L  | н    | L  | н  | н  | н | н | н | н    | н     | н     |

|        | н  | н   | н   | н | н    | н   | L  | н    | н  | н  | н  | Z | Z | Z | Z    | н     | н     |

3-23